## Reduced surface leakage current and trapping effects in AlGaN/GaN high electron mobility transistors on silicon with SiN/Al2O3 passivation

## Reduced surface leakage current and trapping effects in AlGaN/GaN high electron mobility transistors on silicon with SiN/Al<sub>2</sub>O<sub>3</sub> passivation

Z. H. Liu, <sup>1,2,a)</sup> G. I. Ng, <sup>1,2</sup> H. Zhou, <sup>1</sup> S. Arulkumaran, <sup>2</sup> and Y. K. T. Maung <sup>2</sup> School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 <sup>2</sup> Temasek Laboratories, Nanyang Technological University, Singapore 637553

(Received 23 February 2011; accepted 28 February 2011; published online 17 March 2011)

The surface leakage currents and the surface trapping effects of the AlGaN/GaN high electron mobility transistors (HEMTs) on silicon with different passivation schemes, namely, a 120 nm plasma enhanced chemical vapor deposited SiN, a 10 nm atomic layer deposited (ALD)  $Al_2O_3$  and a bilayer of  $SiN/Al_2O_3$  (120/10 nm) have been investigated. After SiN passivation, the surface leakage current of the GaN HEMT was found to increase by about six orders; while it only increased by three orders after the insertion of  $Al_2O_3$  between SiN and AlGaN/GaN. The surface conduction mechanism is believed to be the two-dimensional variable range hopping for all the samples. The leakage current in the etched GaN buffer layer with  $SiN/Al_2O_3$  bilayer passivation was also much smaller than that with only SiN passivation. The pulse measurement shows that the bilayer of  $SiN/Al_2O_3$  passivation scheme can effectively reduce the surface states and suppress the trapping effects. © 2011 American Institute of Physics. [doi:10.1063/1.3567927]

The GaN high electron mobility transistor (HEMT) has been demonstrated to be a promising candidate for high power amplifiers in the microwave communication system and high-voltage power switches. <sup>1,2</sup> Surface passivation is generally necessary to suppress the serious trapping effects such as current collapse and dc-to-rf dispersion due to the large surface states in GaN HEMTs. <sup>3</sup> SiN grown by plasma enhanced chemical vapor deposition (PECVD) system is widely used as the surface passivation dielectric and has been demonstrated to be an effective material to reduce the surface states on GaN or AlGaN. <sup>3</sup> However, The surface leakage current of the GaN HEMT after PECVD SiN passivation depends on the deposition conditions, and it has been observed to obviously increase after passivation. <sup>4,5</sup>

Recently the Al<sub>2</sub>O<sub>3</sub> grown by atomic layer deposition (ALD) system has attracted great interests in the application of GaN metal-insultor-semiconductor HEMTs due to its high dielectric constant, high breakdown field, excellent uniformity and good quality. It has also been demonstrated to be used as a surface passivation layer in the GaN HEMT. We have observed that a thin ALD Al<sub>2</sub>O<sub>3</sub> layer used for the gate dielectric and passivation can increase the 2-dimensional-electron-gas sheet carrier density and drift mobility through the suppression of the trapping effect. In this letter, we report that the high surface leakage current in the GaN HEMT caused by the PECVD SiN passivation can be reduced by inserting a thin ALD Al<sub>2</sub>O<sub>3</sub> layer.

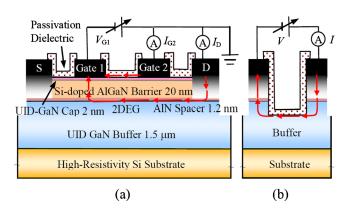

The GaN HEMT structure is shown in Fig. 1. It was grown on a high-resistivity silicon substrate (>6000  $\Omega$  cm) by metal-organic chemical vapor deposition. Its epilayer includes a 2 nm unintentionally doped GaN cap layer, a 17.5 nm Si-doped AlGaN barrier layer, a 1.2 nm AlN spacer layer and a 1.5  $\mu$ m undoped GaN buffer. The fabrication details of the GaN HEMT can be found elsewhere. The device surface was passivated and the electrodes were opened by etching away the dielectric for measurement. Four

The surface leakage currents of the GaN HEMTs with various passivation schemes were measured using the double-gate devices. The circuit configuration for the measurement is shown in Fig. 1(a), similar to the technique reported in Ref. 12. The distances from gate 1 to gate 2 and from gate 2 to drain are 3  $\mu$ m and 2  $\mu$ m, respectively. The gate length and width are 1  $\mu$ m and 50  $\mu$ m, respectively.

FIG. 1. (Color online) (a) Schematic of the passivated AlGaN/GaN HEMT with double gate and the circuit configuration for surface leakage current measurement; (b) schematic of the circuit configuration for etched GaN buffer leakage current measurement.

samples with different passivation schemes were studied: Sample A, without passivation; Sample B, passivated with 120 nm PECVD SiN; Sample C, passivated with 10 nm ALD Al<sub>2</sub>O<sub>3</sub>; Sample D, passivated with a bilayer of 10 nm ALD Al<sub>2</sub>O<sub>3</sub> and 120 nm PECVD SiN. Before passivation, the surface of the samples were carefully treated using ultrasonic acetone and isopropyl alcohol followed by buffered oxide etchant (HF:NH<sub>4</sub>F=1:6.4). The PECVD SiN was deposited with SiH<sub>4</sub>:NH<sub>3</sub>=2:3 at rf power of 20 W and at 300 °C; and the ALD Al<sub>2</sub>O<sub>3</sub> was deposited with trimethylaluminum and H<sub>2</sub>O as precursors at 300 °C. The dc and pulsed current-voltage (*I-V*) measurement were carried out using an HP 4156 semiconductor parameter analyzer and a Diva pulse measurement system, respectively.

a) Electronic mail: liuzhihong@ntu.edu.sg.

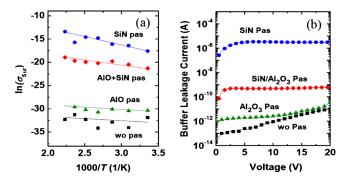

FIG. 2. (Color online) (a) The surface leakage current ( $I_{\rm G2}$ ) and (b) vertical leakage current ( $I_{\rm D}$ ) of the double-gate GaN HEMTs with various passivation schemes under the measurement configuration in Fig. 1.

During the measurement, the gate 2 and drain were biased at 0 V, and the gate 1 was swept from 0 to -20 V. The measurement of the etched GaN buffer leakage current was from two Ohmic contact electrodes fabricated on the AlGaN/GaN mesa with a gap of 5  $\mu$ m and width of 50  $\mu$ m, as shown in Fig. 1(b). Between the two electrodes, the AlGaN/GaN was etched down to a depth around 200 nm.

Figure 2 shows the measured vertical leakage current  $(I_{\rm D})$  and surface leakage current  $(I_{\rm G2})$ . For comparison, the values of the currents at  $V_{\rm g1}$ =-20 V for four samples have also been listed in Table I. Compared to the device without passivation, the SiN passivation has increased the surface leakage current up to six orders. However, the device passivated with 10 nm Al<sub>2</sub>O<sub>3</sub> has a similar value of surface leakage current compared to the unpassivated device. The surface leakage current of the device passivated with the SiN/Al<sub>2</sub>O<sub>3</sub> bilayer is three orders larger than those of the devices unpassivated and passivated with Al<sub>2</sub>O<sub>3</sub>, but three orders smaller than that of the device passivated with only SiN. This means that the surface leakage current of the device with bilayer passivation neither flows along the Al<sub>2</sub>O<sub>3</sub>/nitride semiconductors interface, nor along the Al<sub>2</sub>O<sub>3</sub> bulk, but along the SiN bulk. The 10 nm Al<sub>2</sub>O<sub>3</sub> has blocked part of current injected from the SiN layer to the gate. It can be expected that a thicker Al<sub>2</sub>O<sub>3</sub> can further suppress the surface leakage current in the bilayer passivated device.

The vertical leakage current was also observed to increase after passivation, as shown in Fig. 2(b). For all the samples, the magnitude of  $I_{\rm D}$  is at least one order larger than that of  $I_{\rm G2}$ , indicating that the gate leakage current of the GaN HEMTs is mainly from the vertical path, namely, the Schottky leakage current, instead of the surface path. The increase in the vertical leakage current after passivation is believed to be due to the enhanced electrical line crowding at the drain side of the gate. Similar to the case of the surface

FIG. 3. (Color online) (a) Arrhenius plot of surface leakage conductivity from 25 to 175 °C at  $V_{\rm GI}$ =-20 V; (b) leakage current of the etched GaN buffer with various passivation schemes.

leakage current, the Al<sub>2</sub>O<sub>3</sub> passivated device shows the lowest vertical leakage current among the three passivated devices, whereas the SiN passivated device shows the highest value

To further investigate the physical origin of the surface leakage current, we carried out the temperature dependent *I-V* measurement for the double-gate devices from 25 to 175 °C. The Arrhenius plot of the surface leakage conductivity  $\sigma_{\rm sur}$  is shown in Fig. 3(a). It can be seen that the devices without passivation and with Al<sub>2</sub>O<sub>3</sub> passivation have similar activation energies ( $E_a$ =0.065 eV and  $E_a$ =0.045 eV, respectively, see Table I). It means that the Al<sub>2</sub>O<sub>3</sub> dielectric has not introduced any new surface leakage mechanism. The device with SiN passivation has a much different activation energy  $E_a$ =0.26 eV. In CVD prepared amorphous SiN alloy, typically two activation energies  $E_{\rm al}$ ,  $E_{\rm a2}$  exist in the leakage conductivity, as shown in the following expression: <sup>13</sup>

$$\sigma_{\text{SiN}} = \sigma_1 \exp\left(-\frac{E_{\text{a}1}}{k_{\text{B}}T}\right) + \sigma_2 \exp\left(-\frac{E_{\text{a}2}}{k_{\text{B}}T}\right),$$

where  $E_{\rm a1} > E_{\rm a2}$  and  $E_{\rm a1}$  is typically around 0.7–0.8 eV from the extended state conduction.  $E_{\rm a2}$  is typically around 0.1–0.2 eV from the hopping conduction through the gap-states near the Fermi level. The  $E_{\rm a}$  value of 0.26 eV obtained from our measurement shows that, the surface leakage current after PECVD SiN passivation is due to the hopping conduction through the gap-states near the Fermi leveling in SiN. The device with bilayer passivation has an  $E_{\rm a}$  of 0.14 eV, which is believed to be resulting from the combination of the hopping conduction in SiN and the tunneling conduction across the Al<sub>2</sub>O<sub>3</sub>.

We have also found that a straight line can be fit well for the plot of  $\ln(\sigma_{\rm sur})$  versus  $T^{1/3}$  for all the four samples (the figures are not shown here). This verifies that the conductiv-

TABLE I. Various characteristics for the GaN HEMTs with different passivation schemes.  $[I_{\rm D},\ I_{\rm G2}]$  are the values at  $V_{\rm g1}$ =-20 V;  $I_{\rm buf}$  is the value at V=-20 V.

| Sample No. | Passivation scheme                             | $I_{\rm D} \\ ({\rm mA/mm})$ | $I_{\rm G2}$ (mA/mm) | $E_{\rm a}$ (eV) | $I_{\rm buf} \\ ({\rm mA/mm})$ | $R_{\rm sh} \ (\Omega/{\rm sq})$ | $I_{ m dmax}$ drop at pulsed dc $(\%)$ | $R_{\rm on}$ increase at pulsed dc (%) |

|------------|------------------------------------------------|------------------------------|----------------------|------------------|--------------------------------|----------------------------------|----------------------------------------|----------------------------------------|

| A          | Without passivation                            | $6.1 \times 10^{-5}$         | $1.0 \times 10^{-8}$ | 0.065            | $2.1 \times 10^{-7}$           | 367                              | 59                                     | 72                                     |

| В          | 120 nm PECVD SiN                               | 1.4                          | $1.2 \times 10^{-2}$ | 0.26             | $6.3 \times 10^{-2}$           | 324                              | 0                                      | 0                                      |

| C          | 10 nm ALD Al <sub>2</sub> O <sub>3</sub>       | $5.9 \times 10^{-4}$         | $2.4 \times 10^{-8}$ | 0.045            | $6.1 \times 10^{-7}$           | 325                              | 0                                      | 14                                     |

| D          | SiN/Al <sub>2</sub> O <sub>3</sub> (120/10 nm) | $4.3 \times 10^{-2}$         | $3.9 \times 10^{-5}$ | 0.14             | $1.4 \times 10^{-5}$           | 328                              | 0                                      | 0                                      |

ity of the surface leakage follows the two-dimensional variable range hopping model, as the following expression shows: 12

$$\sigma(T) \propto \exp[-(T_0/T)^{1/3}],$$

where  $T_0$  is the characteristic temperature.

The leakage current of the etched GaN buffer is also important for the actual GaN circuits. Figure 3(b) shows the measured buffer leakage current of the four samples with different passivation schemes. The unpassivated GaN buffer and  $Al_2O_3$  passivated GaN buffer show similar leakage currents at voltage  $> 10\,$  V. The SiN passivation increases the leakage current by more than five orders, and the insertion of a 10 nm  $Al_2O_3$  has lowered down the value by two orders.

To investigate the passivation effect of the various schemes, the sheet carrier resistance  $(R_{sh})$  of the four samples has been measured using van der Pauw patterns, and their values are listed in Table I. The three passivated samples have similar  $R_{\rm sh}$  values, which are ~11% smaller than that of the unpassivated samples. In addition, pulsed *I-V* measurement was performed with pulse width of 200 ns and duty cycle of 0.02%. The I-V characteristics under gate stress bias (e.g., quiescent gate bias  $V_{\rm gq} < V_{\rm th}$ , quiescent drain bias  $V_{\rm dq}$ =0) can be used to check the effect of the surface passivation on the reduction in the surface states.<sup>14</sup> The values of the maximum drain current  $(I_{dmax})$  and on-resistance  $(R_{on})$  at  $V_{qg} = -6$  V,  $V_{dq} = 0$  V have been compared with those values at  $V_{gq}=0$ ,  $V_{dq}=0$  V for all the samples, respectively. The results at  $V_g = 0$  V are listed in Table I. It can be seen that, the  $I_{\text{max}}$  at gate stress has dropped by 59% and  $R_{\text{on}}$  increased by 72% for the unpassivated device. This indicates the existence of the large-density surface states. The Al<sub>2</sub>O<sub>3</sub> passivated device shows no drop of  $I_{\rm dmax}$  but 14% increase in  $R_{\rm on}$ . Whereas the SiN passivated device and the Al<sub>2</sub>O<sub>3</sub>/SiN bilayer passivated device show no change in  $I_{\text{dmax}}$  and  $R_{\text{on}}$ , indicating that only a thin Al<sub>2</sub>O<sub>3</sub> film is not sufficient to serve as a passivation layer. Considering it is timeconsuming for the ALD to deposit a thicker Al<sub>2</sub>O<sub>3</sub> layer and its higher dielectric constant than SiN, the insertion of a thin ALD Al<sub>2</sub>O<sub>3</sub> between the SiN and nitride semiconductor is proposed to be an appropriate passivation scheme to effectively reduce the surface states without the introduction of large surface leakage current.

In conclusion, the PEDCVD SiN passivation has been found to largely increase the surface leakage current for the GaN HEMT, due to the hopping conduction through the gap-states near the Fermi level with  $E_a$ =0.26 eV. The insertion of a thin ALD Al<sub>2</sub>O<sub>3</sub> layer between the PECVD SiN and the nitride semiconductors can effectively reduce the surface leakage current, and meantime maintain the effective passivation effect to reduce the surface states.

The authors would like to thank the Defense Science and Technology Agency of Singapore for the support of this work.

<sup>&</sup>lt;sup>1</sup>U. K. Mishra, L. Shen, T. E. Kazior, and Y. F. Wu, Proc. IEEE **96**, 287 (2008).

<sup>&</sup>lt;sup>2</sup>N. Ikeda, Y. Niiyama, H. Kambayashi, Y. Sato, T. Nomura, S. Kato, and S. Yoshida, Proc. IEEE 98, 1151 (2010).

<sup>&</sup>lt;sup>3</sup>B. M. Green, K. K. Chu, E. M. Chumbes, J. A. Smart, J. R. Shealy, and L. F. Eastman, IEEE Electron Device Lett. **21**, 268 (2000).

<sup>&</sup>lt;sup>4</sup>W. S. Tan, M. J. Uren, P. A. Houston, R. T. Green, R. S. Balmer, and T. Martin, IEEE Electron Device Lett. **27**, 1 (2006).

<sup>&</sup>lt;sup>5</sup>F. Karouta, M. C. J. C. M. Krämer, J. J. M. Kwaspen, A. Grzegorczyk, P. Hageman, B. Hoex, W. M. M. Kessels, J. Klootwijk, E. Timmering, and M. K. Smit, ECS Trans. **16**(7), 181 (2008).

<sup>&</sup>lt;sup>6</sup>P. D. Ye, B. Yang, K. K. Ng, J. Bude, G. D. Wilk, S. Halder, and J. C. M. Hwang, Appl. Phys. Lett. **86**, 063501 (2005).

<sup>&</sup>lt;sup>7</sup>Z. H. Liu, G. I. Ng, S. Arulkumaran, Y. K. T. Maung, K. L. Teo, S. C. Foo, V. Sahmuganathan, T. Xu, and C. H. Lee, IEEE Electron Device Lett. **31**, 96 (2010).

<sup>&</sup>lt;sup>8</sup>Z. H. Liu, G. I. Ng, S. Arulkumaran, Y. K. T. Maung, K. L. Teo, S. C. Foo, and V. Sahmuganathan, IEEE Electron Device Lett. **31**, 803 (2010).

<sup>&</sup>lt;sup>9</sup>D. H. Kim, V. Kumar, G. Chen, A. M. Dabiran, A. M. Wowchak, A. Osinsky, and I. Adesida, Electron. Lett. **43**, 127 (2007).

<sup>&</sup>lt;sup>10</sup>H. Wang, J. W. Chung, X. Gao, S. Guo, and T. Palacios, Phys. Status Solidi 7, 2440 (2010).

<sup>&</sup>lt;sup>11</sup>Z. H. Liu, G. I. Ng, S. Arulkumaran, Y. K. T. Maung, K. L. Teo, S. C. Foo, and V. Sahmuganathan, Appl. Phys. Lett. **95**, 223501 (2009).

<sup>&</sup>lt;sup>12</sup>J. Kotani, M. Tajima, S. Kasai, and T. Hashizume, Appl. Phys. Lett. 91, 093501 (2007).

<sup>&</sup>lt;sup>13</sup>G. Sasaki, S. Fujita, and A. Sasaki, J. Appl. Phys. **54**, 2696 (1983).

<sup>&</sup>lt;sup>14</sup>S. C. Binari, P. B. Klein, and T. E. Kazior, Proc. IEEE **90**, 1048 (2002).